고정 헤더 영역

상세 컨텐츠

본문

산술 논리 장치는 두 숫자의 산술 연산과 논리 연산을 계산하는 회로입니다. (+. -. AND, OR, XOR, XNOR, NOT)

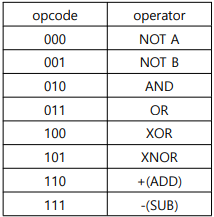

이번에 구현할 산술 논리 장치는 opcode라는 3bit code를 따라서 여러 가지 연산을 하는 장치입니다.

이렇게 계산을 산술연산 혹은 논리연산을 진행한 후에 Calculate Flag가 존재합니다.

Calculate Flag는 산술논리장치에서의 결과의 4가지 상태를 나타냅니다.

C(Carry) : 연산결과가 Carry가 발생하는 경우

N(Negative) : 연산결과가 음수인 경우

Z(Zero) : 연산결과가 0인 경우

V(Overflow) : 연산결과가 overflow가 발생하는 경우

예를 들어서 A와 B를 비교할때 A<B인경우 N=1입니다.

Z=1이고 N=0이면 A와B는 같습니다.

N=0이고 Z=0이면 A>B입니다.

V=1인 경우 최대 bit보다 큰 수가 입력되어 표현할 수 없는 경우입니다.

1. 두개의 양수를 더해서 V=1인경우, A의 최대비트의 전비트의 반전 비트 and B의 최대 비트의 전비트의 반전 비트 and 합의 최대비트의 전비트를 해주어 표현해줍니다.

2. 두개의 음수를 더해서 V=1인 경우는 A의 최대비트의 전비트 and B의 최대비트의 전 비트 and 합의 최대비트의 전비트의 반전비트이다. 전비트를 해주어 표현해줍니다.

위 두 경우를 식으로 나타내면

로 나타낼 수 있습니다.

carry로 또한 나타낼 수 있습니다.

-carry와 overflow의 차이

Carry는 연산도중에 그 비트를 초과할 경우 올림이 발생한 것을 보여주기 위한 flag입니다.

overflow는 2의 보수 표현의 정수 연산에서 부호비트가 변한것을 보여주기 위한 flag입니다.

예를 들면 11+01=00으로 ALU에서 나타나지만 해석해 보면 Unsigned가 아닌 signed로 해석해서 -1+1=0이 되어서 맞는 결과가 됩니다.

Unsigned인지 signed 인지 이것을 구분하려면 C flag나 V flag을 해석해보면 C flag는 unsigned로 해석할때 필요한 것인데 carry flag가 1이되면 거짓이 됩니다.

결론은 overflow bit을 set하는 상황은 MSB가 동일한 두 수를 더했을때 최상위 비트가 바뀌었을 때이고, carry bit을 set하는 상황은 1바이트의 두 값을 더했는데 1바이트 이상의 값이 나왔을때입니다.

「

기초지식(2의보수를 활용한 뺄셈)

2의보수를 활용한 뺄셈

음수로 표현하기 위해서 2의 보수를 활용해야합니다.

1. 각각의 비트를 반전시킵니다.

2. 반전시킨 비트에 1을 더합니다.

+(-3)을 표현하기 위해서는

양수 : 3->0011 => 반전 -> 1100 => 1 더하기 -> 1101 (-3)

」

설계

4-bits CLA to detect overflow

overflow의 유무를 알기 위해서 4-bit Carry Look Ahead에서 Cout과 carry[3]을 출력 할 수 있도록 수정할 수 있게 먼저 설계를 했습니다.

32bits CLA

32-bits CLA도 carry의 최상위 bit 두개를 출력해야하므로 저번시간에 만들었던 32-bit CLA의 마지막을 앞서 설계한 4-bits CLA to detect overflow로 변경했습니다.

맨 마지막 cla4_ov인것을 확인할 수 있고, Cout과 그 전 co를 출력하는것을 확인할 수 있습니다.

Arithmetic logic unit 4 bits

앞선 이론에 OPCODE에 따라서 MUX를 통해 연산을 수행하게 했습니다.

Flag calculator 4 bits

MUX의 결과와 +(add), -(subtraction)의 올림(carry)의 값들을 받아 flag들을 계산합니다.

Flag중 c,z,v는 삼항 연산자(conditional operator)를 사용하여 구현하고, Flag중 n은 sign bit이 0이냐 1이냐에 result의 MSB를 할당했습니다.

이번 testbench는 testvector를 활용해서 검증을 했습니다.

아래와 같은 값을 주었는데

왼쪽 11bits중 왼쪽4bits와 오른쪽 4bits는 11bits중 맨 오른쪽 3bit는 opcode입니다.

_ 뒤에는 예상되는 결과값 4BITS 를 통해서 result_expected와 result를 두어 SELFCHECKING을 할 수 있게 했습니다.

and와 or연산인 010 011이 opcode일때는 Nflags 외에는 다른 FLAGS들은 작동하지 않은 것을 확인할 수 있습니다. opcode가 100일때는 xor연산인데 1111과 1111, 1111과 0000 을 xor해서 먼저 예상했던 결과와 같은것을 확인할 수 있고, 1111과 0000일때 xor은 Nflag만 1이 되었고, 1111과 1111일때는 Zflags만 1이 된것을 확인 할 수 있습니다.

똑같이 1111과 1111, 1111과 0000으로 opcode가 101(xnor)을 했을때 xor과 반대되는 waveform을 확인할 수 있습니다. 마지막으로 opcode가 110(add), 111(sub)일때 Cflags과 Vflags가 작동되는것을 확인할 수 있습니다.

ALU를 통해서 논리연산 뿐만아니라 산술연산도 가능한점이 신기했습니다.

'과제 > 디지털논리회로(verilog)' 카테고리의 다른 글

| D-FlipFlop (0) | 2022.06.22 |

|---|---|

| blocking 과 non-blocking assignment의 차이 (0) | 2022.01.06 |

| CLA(carry-look-ahead) (0) | 2022.01.05 |

| RCA(Ripple Carry Adder) (0) | 2022.01.04 |

| 2-to-1 multiplexer 구현하기 (0) | 2022.01.03 |

댓글 영역